# PCIe/PXIe-5211

# **Counter/Timer Module**

# **User Manual**

User Manual Version:

V1.6.3

Revision Date:

June 17, 2022

| 1.Overview                                                  | 4  |

|-------------------------------------------------------------|----|

| 1.1 Introduction                                            | 4  |

| 1.2 Main Features                                           | 4  |

| 1.3 Abbreviations                                           | 4  |

| 1.4 Learn by Example                                        | 5  |

| 2.Hardware Specifications                                   | 7  |

| 2.1 System Diagram                                          | 7  |

| 2.2 Digital IO Specifications                               | 8  |

| 2.3 Counter/Timer Specifications                            | 9  |

| 2.4 Other Specifications                                    | 10 |

| 2.5 Front Panel and Pin Definition                          | 10 |

| 2.6 Default Routing for Counter Input/Output Signals        | 2  |

| 3.Software                                                  |    |

| 3.1 System Requirements                                     |    |

| 3.2 System Software                                         |    |

| 3.3 C# Programming Language                                 |    |

| 3.4 PCIe/PXIe-5211 Series Hardware Driver                   | 4  |

| 3.5 Install the SeeSharpTools from JYTEK                    | 4  |

| 3.6 Running C# Programs in Linux                            |    |

| 4.Operating PCIe/PXIe-5211                                  |    |

| 4.1 Quick Start                                             |    |

| 4.2 Digital I/O Operations                                  | 6  |

| 4.3 Counter Measurement Operations                          |    |

| 4.3.1 Edge Counting                                         |    |

| 4.3.2 Pulse Measurement                                     |    |

| 4.3.3 Frequency Measurement                                 |    |

| 4.3.4 Period Measurement                                    |    |

| 4.3.5 Two-Edge Separation                                   |    |

| 4.3.6 Quadrature Encoder                                    |    |

| 4.3.7 Two-Pulse Encoder                                     |    |

| 4.4 Counter Generation Operations                           |    |

| Learn by Examples                                           |    |

| 4.5 Clocks                                                  |    |

| 4.5.1 PLL                                                   |    |

| 4.5.2 Sample Clock                                          |    |

| 4.5.3 Timebase                                              |    |

| 4.6 Start Trigger                                           |    |

| 4.7 Logic Level                                             |    |

| 4.8 Multi-Card Synchronization                              |    |

| 4.9 System Synchronization Interface (SSI) for PCIe Modules | 51 |

### Table of Contents

| 4.10 DIP Switch in PCIe-5211                 | 52 |

|----------------------------------------------|----|

| 5.Using PCIe/PXIe-5211 in Other Software     | 53 |

| 5.1 C++                                      | 53 |

| 6.About JYTEK                                | 54 |

| 6.1 JYTEK China                              | 54 |

| 6.2 JYTEK Korea and JYTEK In Other Countries | 54 |

| 6.3 JYTEK Hardware Products                  | 54 |

| 6.4 JYTEK Software Platform                  | 55 |

| 6.5 JYTEK Warranty and Support Services      | 55 |

| 7.Statement                                  | 56 |

| Figure 1 JYPEDIA Information                               | 5   |

|------------------------------------------------------------|-----|

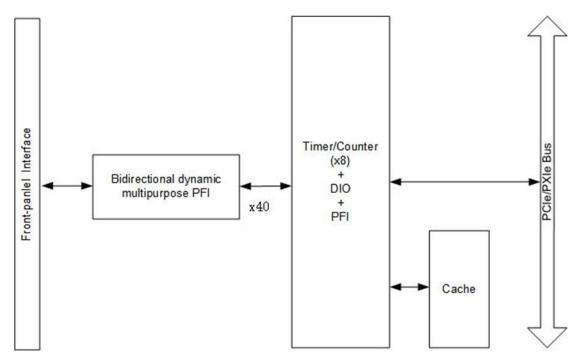

| Figure 2 PCIe/PXIe-5211 Series System Block Diagram        | 7   |

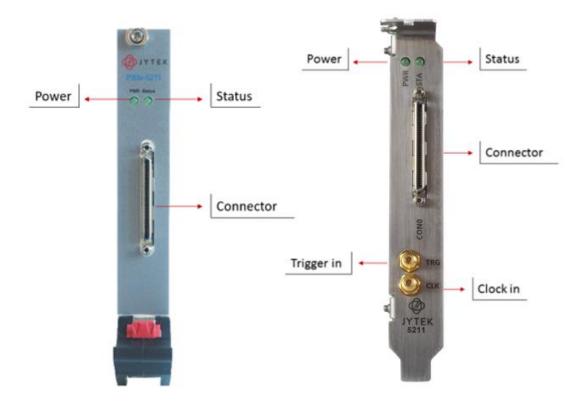

| Figure 3 Front Pannel                                      | .10 |

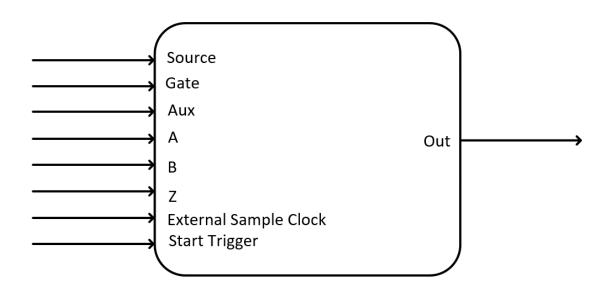

| Figure 4 Counter Input Diagram                             | 7   |

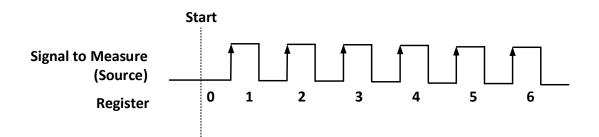

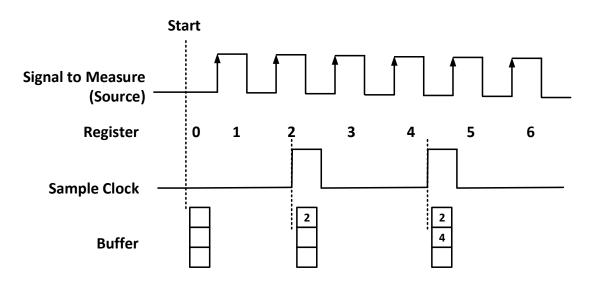

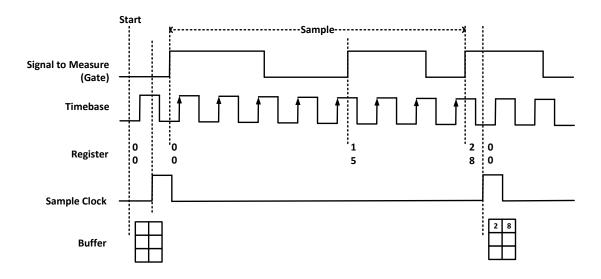

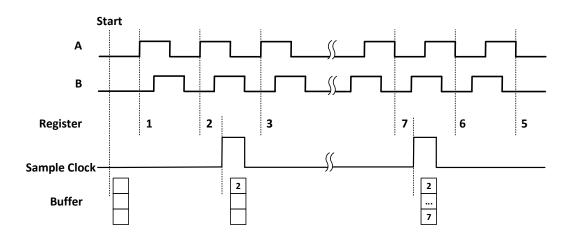

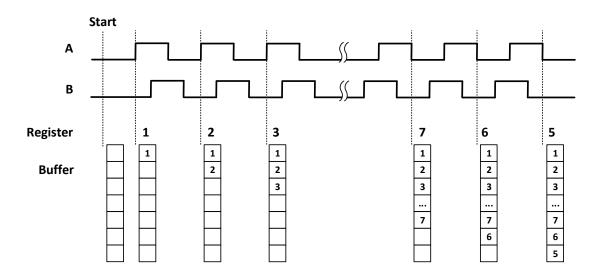

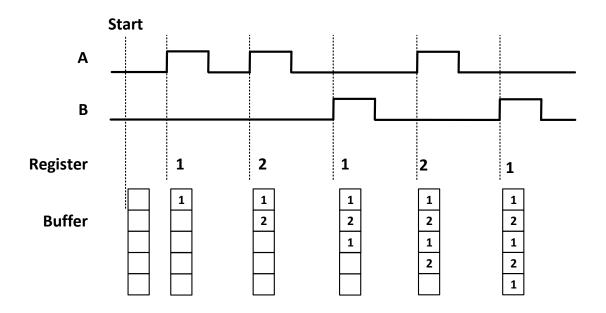

| Figure 5 Simple Edge Counting in Single Mode               | 8   |

| Figure 6 Buffered Edge Counting with Explicit Sample Clock | 8   |

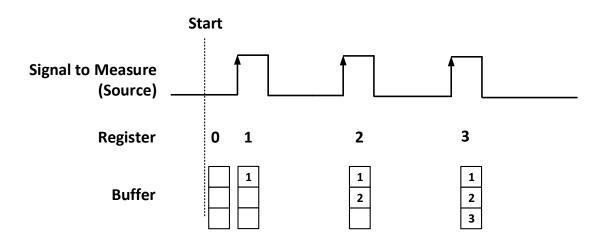

| Figure 7 Simple Edge Counting with Implicit Sample Clock   | 9   |

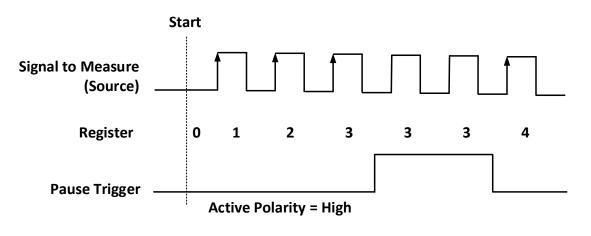

| Figure 8 Pause Trigger                                     | 9   |

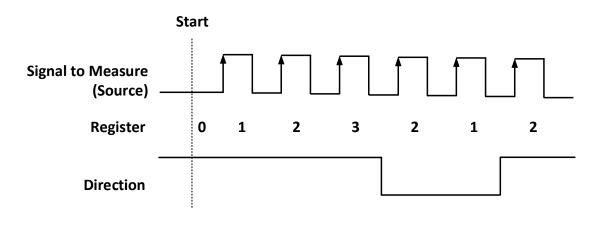

| Figure 9 Count Direction                                   | .10 |

| Figure 10 Edge Counting In Single Mode                     | .11 |

| Figure 11 Edge Counting In Finite Mode                     | .12 |

| Figure 12 Edge Counting In Continuous Mode                 | .12 |

| Figure 13 Edge Counting With Implicit Clock                | .13 |

| Figure 14 Pulse Measurement in Single Mode                 | .14 |

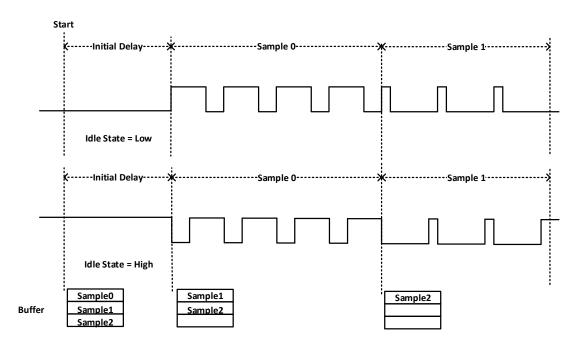

| Figure 15 Pulse Measurement with Explicit Sample Clock     | .15 |

| Figure 16 Pulse Measurement with Implicit Sample Clock     | .15 |

| Figure 17 Pulse Measure In Single Mode                     | .16 |

| Figure 18 Pulse Measure Value In Single Mode               | .17 |

| Figure 19 Pulse Measure In Finite Mode                     | .18 |

| Figure 20 Pulse Measure Values In Finite Mode              | .18 |

| Figure 21 Frequency Measurement with Explicit Sample Clock | .21 |

| Figure 22 Frequency Measure In Single Mode                 | .22 |

| Figure 23 Frequency Measure In Finite Mode                 | .23 |

| Figure 24 Frequency Measure Values In Single Mode          | .24 |

| Figure 25 Period Measure In Single Mode                    | .25 |

| Figure 26 Period Measure In Finite Mode                    | .26 |

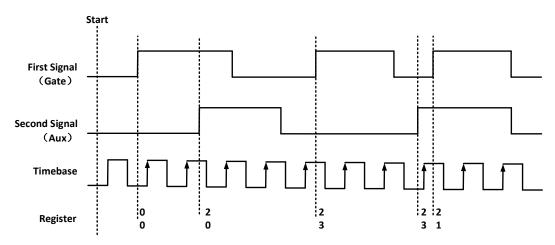

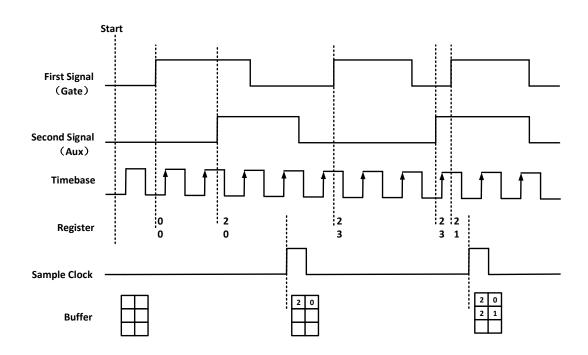

| Figure 27 Two-Edge Separation in Single Mode               | .27 |

| Figure 28 Two-Edge Seperation with Explicit Sample Clock   | .28 |

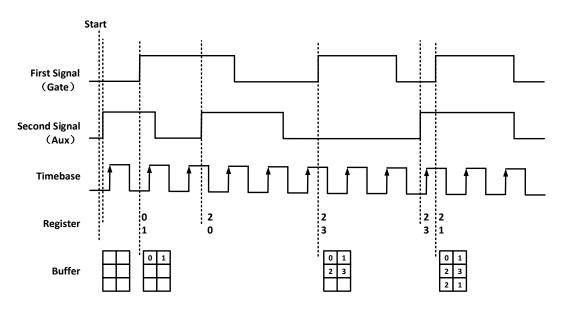

| Figure 29 Two-Edge Seperation with Implicit Sample Clock   | .28 |

|                                                            |     |

| Figure 30 Two-Edge Separation Measure In Single Mode       | 30 |

|------------------------------------------------------------|----|

| Figure 31 Two-Edge Separation Measure In Finite Mode       | 30 |

| Figure 32 Two-Edge Separation Measure In Continuous Mode   | 31 |

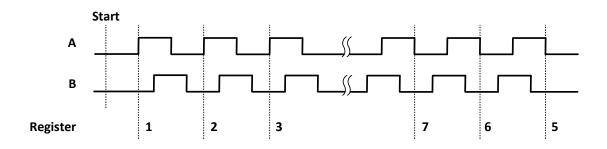

| Figure 33 Quadrature Endcoder x1 Mode                      | 32 |

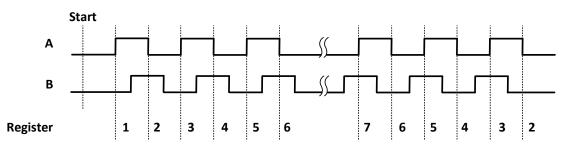

| Figure 34 Quadrature Encoder x2 Mode                       | 32 |

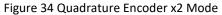

| Figure 35 Quadrature Encoder x4 mode                       | 33 |

| Figure 36 Quadrature Encoder x4 with Explicit Sample Clock | 34 |

| Figure 37 Quadrature Encoder x4 with Implicit Sample Clock | 34 |

| Figure 38 Quadrature Encoder In Single Mode                |    |

| Figure 39 Quadrature Encoder In Finite Mode                | 36 |

| Figure 40 Quadrature Encoder In Continuous Mode            | 36 |

| Figure 41 Two-Pulse Encoder in Single Mode                 | 38 |

| Figure 42 Two-Pulse Encoder with Explicit Sample Clock     | 39 |

| Figure 43 Two-Pulse Encoder with Implicit Sample Clock     | 39 |

| Figure 44 Two-Pulse Encoder In Single Mode                 | 40 |

| Figure 45 Two-Pulse Encoder In Continuous Mode             |    |

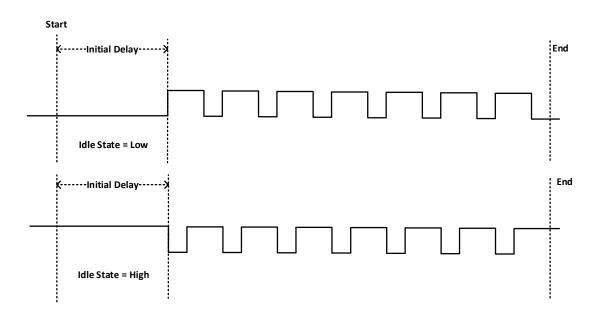

| Figure 46 Pulse Output in Single Mode                      | 42 |

| Figure 47 Pulse Output in Single Mode with Dynamic Update  | 43 |

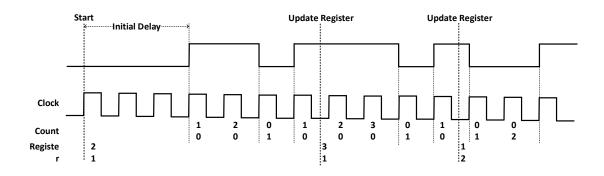

| Figure 48 Buffered Pulse Sequence Generation               | 43 |

| Figure 49 CO In Single Mode                                | 44 |

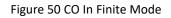

| Figure 50 CO In Finite Mode                                | 45 |

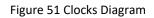

| Figure 51 Clocks Diagram                                   | 46 |

| Figure 52 Rising Edge Digital Trigger                      | 49 |

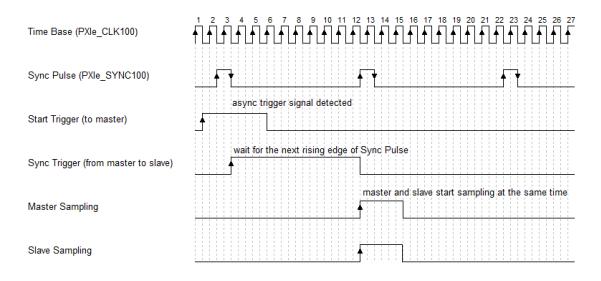

| Figure 53 Master-Slave Synchronization                     | 50 |

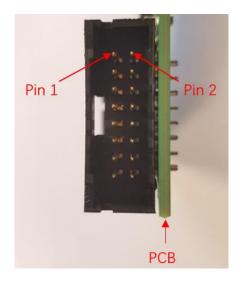

| Figure 54 SSI Connector in PCIe-5211                       | 51 |

| Figure 55 DIP Switch in PCIe-5211                          | 52 |

|                                                            |    |

| Table 1 Digital IO Specifications                            | 8  |

|--------------------------------------------------------------|----|

| Table 2 Counter/Timer Specifications                         | 9  |

| Table 3 Other Specifications                                 | 1  |

| Table 4 Pin Defination                                       | 11 |

| Table 5 Counter Input/Output Default Routing                 | 2  |

| Table 6 Supported Linux Versions                             | 3  |

| Table 7 SSI Connector Pin Assignment for PCIe-5211           | 51 |

| Table 8 Relationship between switch position and slot number | 52 |

# 1. Overview

This chapter presents the information how to use this manual and quick start if you are already familiar with Microsoft Visual Studio and C# programming language.

# **1.1 Introduction**

PCIe/PXIe-5211 series modules are multi-purpose counter data acquisition modules, which can provide 8 channels of counter, supporting edge counting, frequency measurement, period measurement, pulse measurement, two-edge separation measurement, encoder and pulse generation. The device utilizes a high-throughput PCI Express bus and multi-core optimized drivers and application software to provide high-performance capabilities.

Please check with JYTEK website for the latest 5211 series offering.

### 1.2 Main Features

- 8 channels of counter

- 40 channels multi-purpose PFI

- Up to 200MHz internal clock rate

- 1.8 V / 2.5 V / 3.3 V / 5 V level

- Edge Counting / Frequency Measurement / Pulse measurement / Period Measurement / Two-Edge seperation

- Quadrature (x1/x2/x4) encoder

- Two-Pulse encoder

- Dynamic reconfigurable counter output function

- Support multi-card synchronization

- On-board high-performance TCXO clock

- On-board clock generator for sampling

### **1.3 Abbreviations**

- DI: Digital Input

- DO: Digital Output

- CI: Counter Input

- CO: Counter Output

DAQ: Data AcQuisition

### PFI: Programmable Function Interface

TXCO: Temperature Compensate X'tal (crystal) Oscillator

## 1.4 Learn by Example

JYTEK has added **Learn by Example** in this manual. We provide many sample programs for this device. Please download and install the sample programs for this device. You can download a JYPEDIA excel file from our web www.jytel,com. Open JYPEDIA and search for JY5211 in the driver sheet, select **JY5211.Examples.zip**. This will lead you to download the sample program for this device. In addition to the download information, JYPEDIA also has a lot of other valuable information, JYTEK highly recommend you use this file to obtain information from JYTEK.

| А                          | В                 |

|----------------------------|-------------------|

| 简仪科技<br>JYTEK              | Drivers are often |

| Drivers 🖵                  | Update Date 👻     |

| JY5211 V2.0.0 Win.zip      | 2020/9/18         |

| JY5211 V2.0.0 Linux.tar    | 2020/9/18         |

| JY5211 V2.0.0 Examples.zip | 2020/10/21        |

|                            |                   |

|                            |                   |

|                            |                   |

|                            |                   |

#### Figure 1 JYPEDIA Information

In a **Learn by Example** section, the sample program is in bold style such as **Counter Input-->Winform CI Single Edge Counting**; the property name in the sample program is also in bold style such as **SamplesToAcquire**; the technical names used in the manual is in italic style such as *SampleRate*. You can easily relate the property names in the example program with the manual documentation.

In an **Learn by Example** section, the experiment is set up as follow. A PCIe/PXIe-5211 card is plugged in a desktop computer. The PCIe/PXIe-5211 is connected to a TB-68/DIN-68S-01 terminal block. A signal source is also connected to the same terminal block.

The TB-68 has 4 terminal columns, J1 - J4. In the rest of this manual, the wire connection in each **Learn by Example** section will be given by the pin numbers only.

Tip: PCIe/PXIe-5211 also has the counter output capability. If you do not have a signal source, you can use the outputs of PCIe/PXIe-5211 as the signal source. In this case you need first run example program **Counter Output--> Winform CO Continuous Wrapping** to generate the output.

# 2. Hardware Specifications

### 2.1 System Diagram

Figure 2 PCIe/PXIe-5211 Series System Block Diagram

The system block diagram of PCIe/PXIe-5211 series is shown in Figure 2.

It is mainly composed of one DIO module and eight Counter/Timer modules, providing digital input, digital output, counter input, counter output functions. JYTEK's FPGA-based driver FirmDrive provides a stable and efficient PCIe / PXIe / USB interface.

# 2.2 Digital IO Specifications

#### Basic

| Number of channels                          | 40                       |

|---------------------------------------------|--------------------------|

| Ground reference                            | GND                      |

| Direction control                           | Independently Controlled |

| Pull-down resister                          | NONE                     |

|                                             | 1.8 V                    |

|                                             | 2.5 V                    |

| Logic signal levels                         | 3.3 V                    |

|                                             | 5 V                      |

| Input voltage protection                    | -0.5-(UserVcc+0.5 V)     |

| Output impedance                            | 50 Ω                     |

| UserVcc: user select the logic signal level |                          |

#### DIO

| 510            |                   |

|----------------|-------------------|

| Terminals used | DIO <039>         |

| Port width     | 32 bits (Maximum) |

#### PFI

| FII                     |               |

|-------------------------|---------------|

| Available PFI           | PFI<039>      |

|                         | Static input  |

| Supported functions     | Static output |

| Supported functions     | Timing input  |

|                         | Timing output |

| Timing output source    | Counter       |

| Debounce filter options | Not Support   |

Recommended Operating Conditions

| 1.2 V (UserVcc=1.8 V)  |  |  |

|------------------------|--|--|

| 1.7 V (UserVcc=2.5 V)  |  |  |

| 2 V (UserVcc=3.3 V)    |  |  |

| 3.5 V (UserVcc=5 V)    |  |  |

| 0.65 V (UserVcc=1.8 V) |  |  |

| 0.7 V (UserVcc=2.5 V)  |  |  |

| 0.8 V (UserVcc=3.3 V)  |  |  |

| 1.5 V (UserVcc=5 V)    |  |  |

| UserVcc+0.5 V          |  |  |

| -0.5 V                 |  |  |

| -4 mA(UserVcc=1.8 V)   |  |  |

| -8 mA(UserVcc=2.5V)    |  |  |

| -24 mA(UserVcc=3.3 V)  |  |  |

| -32 mA(UserVcc=5 V)    |  |  |

| 4 mA(UserVcc=1.8 V)    |  |  |

| 8 mA(UserVcc=2.5 V)    |  |  |

| 24 mA(UserVcc=3.3 V)   |  |  |

| 32 mA(UserVcc=5 V)     |  |  |

|                        |  |  |

#### Electrical

| Maximum input current of low-level voltage  | -2 μA |

|---------------------------------------------|-------|

| Maximum input current of high-level voltage | 2 μΑ  |

# 2.3 Counter/Timer Specifications

#### Basic

| Number of counters/timers | 8                   |

|---------------------------|---------------------|

| Resolution                | 32 bits             |

|                           | Edge Counting       |

|                           | Frequency           |

|                           | Period              |

| Measurement functions     | Pulse               |

|                           | Two-Edge Separation |

|                           | Quadrature Encoder  |

|                           | Two Pulse Encoder   |

#### Maximum Frequency of the Source

|                       | PFI    |

|-----------------------|--------|

| Frequency Measurement | 50 MHz |

| Edge Counting         | 50 MHz |

#### Minimum Pulse Measurement

|                     | PFI   |

|---------------------|-------|

| Period Measurement  | 15 ns |

| Pulse Measurement   | 20 ns |

| Two-Edge Separation | 20 ns |

#### **Other Functions**

| Position measurement       | Quadrature encoder (x1/x2/x4) with Z reloading; |  |  |  |  |

|----------------------------|-------------------------------------------------|--|--|--|--|

|                            | Two-pulse encoder                               |  |  |  |  |

| Output applications        | Pulse Generation with Dynamic Update            |  |  |  |  |

|                            | Buffered Pulse Sequence Generation              |  |  |  |  |

|                            | 200 MHz,                                        |  |  |  |  |

| Internal timebase          | 5 MHz,                                          |  |  |  |  |

|                            | 100 kHz                                         |  |  |  |  |

| Internal timebase accuracy | 2 ppm                                           |  |  |  |  |

| External timebase          | 0-50 MHz                                        |  |  |  |  |

|                            | Gate                                            |  |  |  |  |

|                            | Source                                          |  |  |  |  |

| Counter input              | AUX                                             |  |  |  |  |

|                            | A, B, Z                                         |  |  |  |  |

|                            | Start Trigger                                   |  |  |  |  |

|                            | External Sample Clock                           |  |  |  |  |

#### Table 2 Counter/Timer Specifications

# 2.1 Front Panel and Pin Definition

Figure 3 Front Pannel

|                               | SCSI-VHD | CI 68pir | 1                              |

|-------------------------------|----------|----------|--------------------------------|

| Signal                        | Pin      | Pin      | Signal                         |

| PFI30 / DIO 30 / CTR 7 Aux    | 35       | 1        | PFI31 / DIO 31 / CTR 7 Out     |

| GND                           | 36       | 2        | GND                            |

| PFI28 / DIO 28 / CTR 7 Source | 37       | 3        | PFI29 / DIO 29 / CTR 7 Gate    |

| GND                           | 38       | 4        | GND                            |

| PFI26 / DIO 26 / CTR 6 Aux    | 39       | 5        | PFI27 / DIO 27 / CTR 6 Out     |

| GND                           | 40       | 6        | GND                            |

| PFI24 / DIO 24 / CTR 6 Source | 41       | 7        | PFI25 / DIO 25 / CTR 6 Gate    |

| GND                           | 42       | 8        | PFI32 / DIO 32 / Start Trigger |

| PFI22 / DIO 22 / CTR 5 Aux    | 43       | 9        | PFI23 / DIO 23 / CTR 5 Out     |

| GND                           | 44       | 10       | GND                            |

| PFI20 / DIO 20 / CTR 5 Source | 45       | 11       | PFI21 / DIO 21 / CTR 5 Gate    |

| GND                           | 46       | 12       | GND                            |

| PFI18 / DIO 18 / CTR 4 Aux    | 47       | 13       | PFI19 / DIO 19 / CTR 4 Out     |

| GND                           | 48       | 14       | GND                            |

| PFI16 / DIO 16 / CTR 4 Source | 49       | 15       | PFI17 / DIO 17 / CTR 4 Gate    |

| GND                           | 50       | 16       | GND                            |

| PFI14 / DIO 14 / CTR 3 Aux    | 51       | 17       | PFI15 / DIO 15 / CTR 3 Out     |

| PFI33 / DIO 33 / ECLK         | 52       | 18       | GND                            |

| PFI12 / DIO 12 / CTR 3 Source | 53       | 19       | PFI13 / DIO 13 / CTR 3 Gate    |

| GND                           | 54       | 20       | GND                            |

| PFI10 / DIO 10 / CTR 2 Aux    | 55       | 21       | PFI11 / DIO 11 / CTR 2 Out     |

| GND                           | 56       | 22       | GND                            |

| PFI8 / DIO 8 / CTR 2 Source   | 57       | 23       | PFI9 / DIO 9 / CTR 2 Gate      |

| GND                           | 58       | 24       | GND                            |

| PFI6 / DIO 6 / CTR 1 Aux      | 59       | 25       | PFI7 / DIO 7 / CTR 1 Out       |

| PFI35 / DIO 35                | 60       | 26       | PFI34 / DIO 34                 |

| PFI4 / DIO 4 / CTR 1 Source   | 61       | 27       | PFI5 / DIO 5 / CTR 1 Gate      |

| GND                           | 62       | 28       | GND                            |

| PFI2 / DIO 2 / CTR 0 Aux      | 63       | 29       | PFI3 / DIO 3 / CTR 0 Out       |

| PFI37 / DIO 37                | 64       | 30       | PFI36 / DIO 36                 |

| PFI0 / DIO 0 / CTR 0 Source   | 65       | 31       | PFI1 / DIO 1 / CTR 0 Gate      |

| GND                           | 66       | 32       | GND                            |

| PFI39 / DIO 39                | 67       | 33       | PFI38 / DIO 38                 |

| GND                           | 68       | 34       | GND                            |

Table 3 Pin Defination

# 2.2 Other Specifications

### PLL(Phase lock loop)

| Number of PLL          | 1                             |  |  |  |

|------------------------|-------------------------------|--|--|--|

|                        | PXIe_DSTAR A: 100 MHz (Max)   |  |  |  |

| Reference clock source | PXIe_CLK100: 100 MHz          |  |  |  |

|                        | Onboard TCXO: 10 MHz          |  |  |  |

|                        | 200 MHz base clock            |  |  |  |

|                        | Counter internal sample clock |  |  |  |

| Output                 | 100 KHz timebase              |  |  |  |

|                        | 5 MHz timebase                |  |  |  |

|                        | 200 MHz timebase              |  |  |  |

#### тсхо

|                | Nominal frequency                  | 10 MHz     |

|----------------|------------------------------------|------------|

| Pasic Property | Warm-up time                       | 15 minutes |

| Basic Property | Temperature drift                  | ±20 ppb    |

|                | Temperature drift and 1 year drift | ±0.5 ppm   |

#### External Digital Trigger

| External Digital Hig            |                          |                      |  |  |

|---------------------------------|--------------------------|----------------------|--|--|

|                                 |                          | PXI_TRIG <07>        |  |  |

|                                 | Trigger source           | PXI_STAR             |  |  |

| Trigger functions               |                          | PFI<039>             |  |  |

|                                 | Polarity                 | Rising Edge          |  |  |

|                                 | Counter/Timer functions  | Start trigger        |  |  |

| Device to device<br>trigger bus | Input course             | PXI_TRIG <07>        |  |  |

|                                 | Input source             | PXI_STAR             |  |  |

|                                 | Output destination       | PXI_TRIG <07>        |  |  |

|                                 | Output options           | Sync Trigger Routing |  |  |

|                                 | Debounce filter settings | Not Support          |  |  |

#### Bus and Power

|               | PXIe standard                    | x4 PXI Express peripheral module<br>Specification V1.0 compliant |

|---------------|----------------------------------|------------------------------------------------------------------|

| Bus interface | Slot supported                   | x1 and x4 PXI Express or PXI<br>Express hybrid slots             |

| Calibration   | Recommended warm-up time         | >=15 min                                                         |

| Calibration   | Recommended calibration interval | One year                                                         |

#### Physical Size and Environment

| Size                     | External physical size    | 3U PXIe                   |

|--------------------------|---------------------------|---------------------------|

| Size                     | Weight                    | 190 g                     |

| Operating Indoor only    |                           | Yes                       |

| Operating<br>Environment | Ambient temperature range | 0 °C to 50 °C             |

| Environment              | Relative humidity range   | 20% to 80%, noncondensing |

| Storage                  | Ambient temperature range | -20 °C to 80 °C           |

| Environment              | Relative humidity range   | 10% to 90%, noncondensing |

Table 4 Other Specifications

# 2.3 Default Routing for Counter Input/Output Signals

All counter input and output terminals are routed to a certain PFI by default as shown in Table 5.

| Application                              | Signal Type                       | Ctr0     | Ctr1       | Ctr2  | Ctr3  | Ctr4  | Ctr5  | Ctr6  | Ctr7  |

|------------------------------------------|-----------------------------------|----------|------------|-------|-------|-------|-------|-------|-------|

|                                          | Signal To Measure(Source)         | PFIO     | PFI4       | PFI8  | PFI12 | PFI16 | PFI20 | PFI24 | PFI28 |

| Educ Counting                            | Pause Trigger(Gate)               | PFI1     | PFI5       | PFI9  | PFI13 | PFI17 | PFI21 | PFI25 | PFI29 |

| Edge Counting                            | Count Direction(Aux)              | PFI2     | PFI6       | PFI10 | PFI14 | PFI18 | PFI22 | PFI26 | PFI30 |

|                                          | Output(Out)                       | PFI3     | PFI7       | PFI11 | PFI15 | PFI19 | PFI23 | PFI27 | PFI31 |

| Frequency Measurement                    | Signal To Measure(Gate)           | PFI1     | PFI5       | PFI9  | PFI13 | PFI17 | PFI21 | PFI25 | PFI29 |

| Frequency measurement                    | External Timebase(Source)         | PFIO     | PFI4       | PFI8  | PFI12 | PFI16 | PFI20 | PFI24 | PFI28 |

| Period Measurement                       | Signal To Measure(Gate)           | PFI1     | PFI5       | PFI9  | PFI13 | PFI17 | PFI21 | PFI25 | PFI29 |

|                                          | External Timebase(Source)         | PFI0     | PFI4       | PFI8  | PFI12 | PFI16 | PFI20 | PFI24 | PFI28 |

| Pulse Measurement                        | Signal To Measure(Gate)           | PFI1     | PFI5       | PFI9  | PFI13 | PFI17 | PFI21 | PFI25 | PFI29 |

| Puise Measurement                        | External Timebase(Source)         | PFI0     | PFI4       | PFI8  | PFI12 | PFI16 | PFI20 | PFI24 | PFI28 |

|                                          | First Signal (Gate)               | PFI1     | PFI5       | PFI9  | PFI13 | PFI17 | PFI21 | PFI25 | PFI29 |

| Two-Edge Separation Measurement          | Second Signal (Aux)               | PFI2     | PFI6       | PFI10 | PFI14 | PFI18 | PFI22 | PFI26 | PFI30 |

|                                          | External Timebase(Source)         | PFI0     | PFI4       | PFI8  | PFI12 | PFI16 | PFI20 | PFI24 | PFI28 |

|                                          | A Signal (A )                     | PFI0     | PFI4       | PFI8  | PFI12 | PFI16 | PFI20 | PFI24 | PFI28 |

| Quad Encoder                             | B Signal(B)                       | PFI2     | PFI6       | PFI10 | PFI14 | PFI18 | PFI22 | PFI26 | PFI30 |

|                                          | Z Signal(Z)                       | PFI1     | PFI5       | PFI9  | PFI13 | PFI17 | PFI21 | PFI25 | PFI29 |

| Two-Pulse Encoder                        | A Signal (A )                     | PFI0     | PFI4       | PFI8  | PFI12 | PFI16 | PFI20 | PFI24 | PFI28 |

| Iwo-Puise Elicouel                       | B Signal(B)                       | PFI2     | PFI6       | PFI10 | PFI14 | PFI18 | PFI22 | PFI26 | PFI30 |

| Pulse Generation                         | Output(Out)                       | PFI3     | PFI7       | PFI11 | PFI15 | PFI19 | PFI23 | PFI27 | PFI31 |

|                                          | External Timebase(Source)         | PFIO     | PFI4       | PFI8  | PFI12 | PFI16 | PFI20 | PFI24 | PFI28 |

| Note: Start Trigger: PFI 32 (For all Cou | inter), External Sample Clock: PF | 133 (For | all Counte | er)   |       |       |       |       |       |

Table 5 Counter Input/Output Default Routing

# 3. Software

## 3.1 System Requirements

PCIe/PXIe-5211 modules can be used in a Windows or a Linux operating system.

Microsoft Windows: Windows 7 32/64 bit, Windows 10 32/64 bit.

Linux Kernel Versions: There are many Linux versions. It is not possible JYTEK can support and test our devices under all different Linux versions. JYTEK will at the best support the following Linux versions.

| Linux Version                                                   |

|-----------------------------------------------------------------|

| Ubuntu LTS                                                      |

| 16.04: 4.4.0-21-generic(desktop/server)                         |

| 16.04.6: 4.15.0-45-generic(desktop) 4.4.0-142-generic(server)   |

| 18.04: 4.15.0-20-generic(desktop) 4.15.0-91-generic(server)     |

| 18.04.4: 5.3.0-28-generic (desktop) 4.15.0-91-generic(server)   |

| Localized Chinese Version                                       |

| 中标麒麟桌面操作系统软件(兆芯版)V7.0(Build61): 3.10.0-862.9.1.nd7.zx.18.x86_64 |

| 中标麒麟高级服务器操作系统软件V7.0U6: 3.10.0-957.el7.x86_64                    |

Table 6 Supported Linux Versions

# 3.2 System Software

When using the PCIe/PXIe-5211 in the Window environment, you need to install the following software from Microsoft website:

Microsoft Visual Studio Version 2015 or above,

.NET Framework version is 4.0 or above.

.NET Framework is coming with Windows 10. For Windows 7, please check .NET Framework version and upgrade to 4.0 or later version.

Given the resources limitation, JYTEK only tested PCIe/PXIe-5211 with .NET Framework 4.0 with Microsoft Visual Studio 2015. JYTEK relies on Microsoft to maintain the compatibility for the newer versions.

### 3.3 C# Programming Language

All JYTEK default programming language is Microsoft C#. This is Microsoft recommended programming language in Microsoft Visual Studio and is particularly

suitable for the test and measurement applications. C# is also a cross platform programming language.

### 3.4 PCIe/PXIe-5211 Series Hardware Driver

After installing the required application development environment as described above, you need to install the PCIe/PXIe-5211 hardware driver.

JYTEK hardware driver has two parts: the shared common driver kernel software (FirmDrive) and the specific hardware driver.

Common Driver Kernel Software (FirmDrive): FirmDrive is the JYTEK's kernel software for all hardware products of JYTEK instruments. You need to install the FirmDrive software before using any other JYTEK hardware products. FirmDrive only needs to be installed once. After that, you can install the specific hardware driver.

Specific Hardware Driver: Each JYTEK hardware has a C# specific hardware driver. This driver provides rich and easy-to-use C# interfaces for users to operate various PCIe/PXIe-5211 function. JYTEK has standardized the ways which JYTEK and other vendor's DAQ boards are used by providing a consistent user interface, using the methods, properties and enumerations in the object-oriented programming environment. Once you get yourself familiar with how one JYTEK DAQ module works, you should be able to know how to use all other DAQ hardware by using the same methods.

# 3.5 Install the SeeSharpTools from JYTEK

To efficiently and effectively use PCIe/PXIe-5211 boards, you need to install a set of free C# utilities, SeeSharpTools from JYTEK. The SeeSharpTools offers rich user interface functions you will find convenient in developing your applications. They are also needed to run the examples come with PCIe/PXIe-5211 hardware. Please register and down load the latest SeeSharpTools from our website, www.jytek.com.

# 3.6 Running C# Programs in Linux

Most C# written programs in Windows can be run by MonoDevelop development system in a Linux environment. You would develop your C# applications in Windows using Microsoft Visual Studio. Once it is done, run this application in the MonoDevelop environment. This is JYTEK recommended way to run your C# programs in a Linux environment.

If you want to use your own Linux development system other than MonoDevelop, you can do it by using our Linux driver. However, JYTEK does not have the capability to

support the Linux applications. JYTEK completely relies upon Microsoft to maintain the cross-platform compatibility between Windows and Linux using MonoDevelop.

# 4. Operating PCIe/PXIe-5211

This chapter provides the operation guides for PCIe/PXIe-5211, including Timer and programmable I/O interface, etc.

JYTEK provides extensive examples, on-line help and documentation to assist you to use the PCIe/PXIe-5211 module. JYTEK strongly recommends you go through these examples before writing your own application. In many cases, an example can also be a good starting point for a user application.

# 4.1 Quick Start

After you have installed the driver software and the SeeSharpTools, you are ready to use Microsoft Visual Studio C# to operate the PCIe/PXIe-5211 products.

If you are already familiar with Microsoft Visual Studio C#, the quickest way to use PCIe/PXIe-5211 boards is to go through our extensive examples. We provide source code of our examples. In many cases, you can modify the source code and start to write your applications.

# 4.1 Digital I/O Operations

The PCIe/PXIe-5211 provides programable I/O function, and contains 40 channels of Programmable Function Interface (PFI).

All 40 PFIs can be used as static digital inputs or outputs. The direction and output state of each PFI can be controlled independently. Users can configure these PFIs by the driver.

In addition, the PCIe/PXIe-5211 also provides an Debounce Filter for each PFI, effectively eliminate the false pulse signal introduced by jitter.

Set JY5211CITask.Device.PFI.Filter.Enable to use this function.

This function enables the filter on Specified Group of Terminals and set the minPulseWidth (ns) of a specified length. Jitter smaller than this length will be ignored. The minPulseWidth is 8 ns in the range of 8 ns to 2040 ns, 128 ns in the range of 2040 ns to 32640 ns, and 2048 ns in the range of 32640 ns to 522240 ns

# **4.2 Counter Measurement Operations**

The PCIe/PXIe-5211 has eight identical 32-bit channels of timer/counter as shown in Figure 4.

#### Figure 4 Counter Input Diagram

Each counter has eight input terminals and one output terminal, and these terminals have different functions in different counter measurement application described below:

- Edge Counting

- Pulse Measurement

- Frequency Measurement

- Period Measurement

- Two-Edge Separation

- Quadrature Encoder (x1, x2, x4)

- Two-Pulse Encoder

For buffered acquisition, each counter has a separate DDR storage space and requires a sample clock. For more information about sample clock, please refer to chapter 4.4.2.

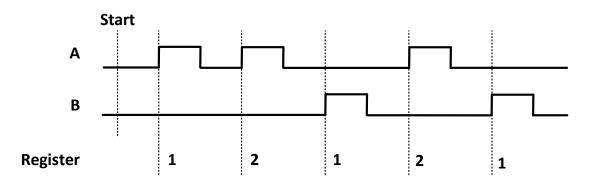

### 4.2.1 Edge Counting

The counter counts the number of active edges of input signal. Default, the input signal must be connected to Counter Source terminal.

Set JY5211CITask.Type to CIType.EdgeCounting to use this function.

### Timing

1) Single Mode

The counting value is written to the register on each rising edge or falling edge of the measured signal as shown in Figure 5.

Figure 5 Simple Edge Counting in Single Mode

To configure the counter to work in this mode, set JY5211CITask.Mode to CIMode.Single.

2) Finite/Continuous Mode with Explicit Sample Clock

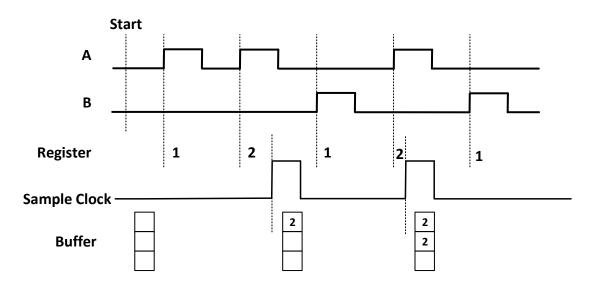

The counting value is stored into the buffer on each rising edge of the sample clock as shown in Figure 6.

Figure 6 Buffered Edge Counting with Explicit Sample Clock

To configure the counter to work in this mode, set JY5211CITask.Mode to CIMode.Finite or CIMode.Continuous, and set JY5211CITask.SampleClock.Source to CISampleClockSource.Internal or CISampleClockSource.External.

3) Finite/Continuous Mode with Implicit Sample Clock

In implicit mode, the signal active edge as the implicit sample clock edge. The counting value is stored into the buffer on each rising edge of the measured signal as shown in Figure 7.

Figure 7 Simple Edge Counting with Implicit Sample Clock

To configure the counter to work in this mode, set JY5211CITask.Mode to CIMode.Finite or CIMode.Continuous, and set JY5211CITask.SampleClock.Source to CISampleClockSource.Implicit.

### Pause Trigger

Pause trigger is used to pause counting when the input signal is active depending on active polarity configuration as shown in Figure 8. Default, the Pause Trigger signal must be connected to Counter Gate terminal.

Figure 8 Pause Trigger

To cofigure the pause trigger, use the properties as below:

JY5211CITask.EdgeCounting.Pause.ActivePolarity – To set active level (high or low) to pause counting.

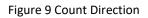

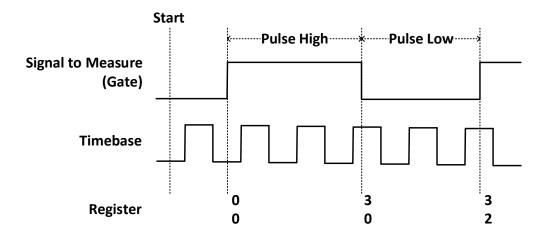

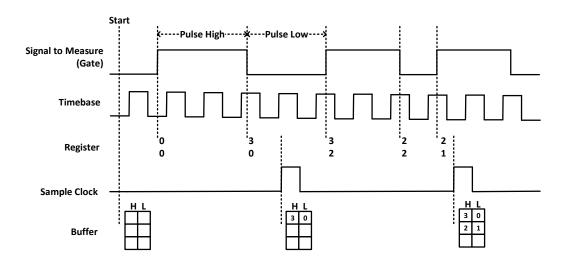

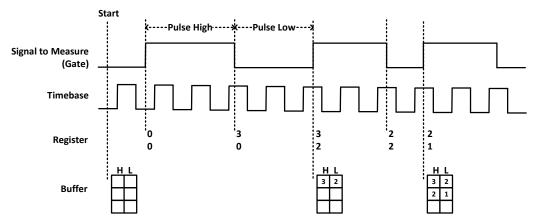

### **Count Direction**

User can control the counting direction through software configuration or by an external input signal. Default, the external control direction signal must be connected to Counter Aux terminal.

When using an input signal to control the counting direction, the counter counts up when the signal is high and counts down when the signal is low as shown in Figure 9.

To cofigure the count direction, use the properties as belows:

JY5211CITask.EdgeCounting.Direction – To specify count up, count down, or controled by an external signal.

### **Exporting Count Event**

When the counting value reaches the specified threshold, the counter will generate a pulse. To change the threshold, using following property:

• JY5211CITask.EdgeCounting.OutEvent.Threshold

### Terminals

To change the terminal of signals instead of using its default value as shown in chapter 2.3, using following properties:

- JY5211CITask.EdgeCounting.InputTerminal Signal-to-measure input terminal.

- JY5211CITask.EdgeCounting.Pause.Terminal Pause signal input terminal.

- JY5211CITask.EdgeCounting.DirTerminal External direction control signal input terminal.

- JY5211CITask.EdgeCounting.OutEvent.Terminal Count event output terminal.

#### Learn by Examples 4.2.1

- Connect the signal source's positive terminal Ch1 of a signal source to PCIe/PXIe-5211 counterO's edge counting source (CTR0\_Source, Pin#65), negative terminal to the ground (GND, Pin#66) as shown in Table 2-15 Pin Defination. (CTR0\_Source, GND) consists of an edge counting counter input.

- Set the signal source Ch1's output to squarewave signal (f=1Hz,  $V_H$ =3.3v,  $V_L$ =0v).

### Single Mode

Open Counter Input-->Winform CI Single EdgeCounter, set the following numbers as shown:

| PCIe/PXIe-52                            | 11 CI      | Edge | Cour              | nting in                                | n Sing                            | le                                 |                          |

|-----------------------------------------|------------|------|-------------------|-----------------------------------------|-----------------------------------|------------------------------------|--------------------------|

| Slot Number<br>Counter<br>Initial Count | 0          | ~    | Counter<br>Number | Signal to Measure(Source)<br>(Name/Pin) | Pause Trigger(Gate)<br>(Name/Pin) | Count Direction(Aux)<br>(Name/Pin) | Output(Out<br>(Name/Pin) |

| Active Edge                             | Rising     | ~    | CtrO              | PFI0/65                                 | PF11/31                           | PF12/63                            | PF13/29                  |

| Direction                               | CountUp    | ~    | Ctr1              | PFI4/61                                 | PFI5/27                           | PFI6/59                            | PF17/25                  |

| Pause Active Polarity                   | HighLevel  | ~    | Ctr2              | PF18/57                                 | PFI9/23                           | PF110/55                           | PFI11/21                 |

| Out Event Threshold                     | 4294967295 | ÷    | Ctr3              | PFI12/53                                | PF(13/19                          | PF114/51                           | PFU5/17                  |

| Count                                   |            |      | Ctr4              | PFI16/49                                | PFI17/15                          | PF118/47                           | PFI19/13                 |

| count                                   |            |      | Ctr5              | PFI20/45                                | PF(21/11                          | PF122/43                           | PFI23/9                  |

|                                         |            | Ctr6 | PFI24/41          | PFI25/7                                 | PF(26/39                          | PF(27/5                            |                          |

| Start Sto                               | P          |      | Ctr7              | PFI28/37                                | PFI29/3                           | PF(30/35                           | PFI31/1                  |

#### Figure 10 Edge Counting In Single Mode

- Count direction is set by Direction.

- > The table in the sample program is a connection diagram for your convenience.

- Click Start, and the result is shown by Count. In this example Count increases by 1 every second for a 1Hz squarewave.

#### Finite/Continuous Mode

■ Change the squarewave frequency to 50 Hz.

Open Counter Input-->Winform CI Finite/Continuous Edge Counting, set the following numbers as shown:

| PCle/PXle-5211 Cl Edge Counting in | Finite Mode |               |     |                                        |                                      | _                                  |                           |

|------------------------------------|-------------|---------------|-----|----------------------------------------|--------------------------------------|------------------------------------|---------------------------|

| PCI                                | [e/PXIe     | -5211         | CI  | Edge Co                                | ounting                              | in Fini                            | te                        |

| Slot Number                        | 0           |               |     |                                        |                                      |                                    |                           |

| Counter                            | 0           | $\overline{}$ |     |                                        |                                      |                                    |                           |

| Initial Count                      | 0           | •             |     |                                        |                                      |                                    |                           |

| Active Edge                        | Rising      | ✓             |     |                                        |                                      |                                    |                           |

| Direction                          | CountUp     | $\overline{}$ |     |                                        |                                      |                                    |                           |

| Pause Active Polarity              | HighLevel   | -<br>-        |     |                                        |                                      |                                    |                           |

| Sample Clock Source                | Internal    | $\overline{}$ |     |                                        |                                      |                                    |                           |

| Sample Rate                        | 10          | ÷             |     |                                        |                                      |                                    |                           |

| External Sample Clock Terminal     | PFI33       | ~             |     |                                        |                                      |                                    |                           |

| Samples to Acquire                 | 10          | •             |     |                                        |                                      |                                    |                           |

| Out Event Threshold                | 4294967295  | ÷             |     |                                        |                                      |                                    |                           |

|                                    |             | Cou<br>Nun    |     | Signal to Measure(Source<br>(Name/Pin) | e) Pause Trigger(Gate)<br>(Name/Pin) | Count Direction(Aux)<br>(Name/Pin) | Output(Out)<br>(Name/Pin) |

|                                    |             |               | trO | PFI0/65                                | PFI1/31                              | PFI2/63                            | PFI3/29                   |

|                                    |             |               | tr1 | PFI4/61                                | PFI5/27                              | PFI6/59                            | PFI7/25                   |

|                                    |             |               | tr2 | PFI8/57                                | PF19/23                              | PFI10/55                           | PFI11/21                  |

| Shunt St                           |             |               | tr3 | PFI12/53                               | PFI13/19                             | PFI14/51                           | PFI15/17                  |

| Start St                           |             |               | tr4 | PFI16/49                               | PFI17/15                             | PFI18/47                           | PFI19/13                  |

|                                    |             |               | tr5 | PFI20/45                               | PFI21/11                             | PF122/43                           | PFI23/9                   |

|                                    |             |               | tr6 | PFI24/41                               | PFI25/7                              | PFI26/39                           | PFI27/5                   |

|                                    |             | 0             | tr7 | PFI28/37                               | PFI29/3                              | PFI30/35                           | PFI31/1                   |

| Available Samples: 0               |             |               |     |                                        |                                      |                                    |                           |

Figure 11 Edge Counting In Finite Mode

- > The table in the sample program is a connection diagram for your convenience.

- > Direction is set by **Direction**.

- There are three sample clock sources in PCIe/PXIe-5211 set by Sample Clock Source: Internal, Implicit and External.

| PCI                           | e/PXIe     | -521     | 1 CI              | Edge Count                              | ing in F                          | inite                              |                      |

|-------------------------------|------------|----------|-------------------|-----------------------------------------|-----------------------------------|------------------------------------|----------------------|

|                               |            |          | Index             |                                         | Counts                            |                                    |                      |

| Slot Number                   | 0          |          | 0                 |                                         | 10                                |                                    |                      |

|                               | <u> </u>   |          | 1                 |                                         | 20                                |                                    |                      |

| ounter                        | 0 \        |          | 2                 |                                         | 30                                |                                    |                      |

|                               |            |          | 3                 |                                         | 40                                |                                    |                      |

| Initial Count                 | 0          | -        | 4                 |                                         | 50                                |                                    |                      |

| ctive Edge                    | Rising     |          |                   |                                         |                                   |                                    |                      |

| CTIVE Fuge                    | Rising     | <u> </u> | 5                 |                                         | 60                                |                                    |                      |

| irection                      | CountUp    |          | 6                 |                                         | 70                                |                                    |                      |

|                               | countop    |          | 7                 |                                         | 80                                |                                    |                      |

| ause Active Polarity          | None       |          | 8                 |                                         | 90                                |                                    |                      |

|                               |            |          | 9                 |                                         | 100                               |                                    |                      |

| ample Clock Source            | Internal   |          | -                 |                                         |                                   |                                    |                      |

|                               |            |          |                   |                                         |                                   |                                    |                      |

| Sample Rate                   | 10         |          |                   |                                         |                                   |                                    |                      |

| xternal Sample Clock Terminal | PFI33      |          |                   |                                         |                                   |                                    |                      |

| Samples to Acquire            | 10         |          |                   |                                         |                                   |                                    |                      |

| ut Event Threshold            | 4294967295 | 3        | Counter<br>Number | Signal to Measure(Source)<br>(Name/Pin) | Pause Trigger(Gate)<br>(Name/Pin) | Count Direction(Aux)<br>(Name/Pin) | Output(O<br>(Name/Pi |

|                               |            |          | Ctr0              | PFI0/65                                 | PFI1/31                           | PFI2/63                            | PFI3/29              |

|                               |            |          | Ctr1              | PFI4/61                                 | PFI5/27                           | PFI6/59                            | PF17/25              |

|                               |            |          | Ctr2              | PFI8/57                                 | PFI9/23                           | PFI10/55                           | PFI11/21             |

|                               |            |          | Ctr3              | PFI12/53                                | PFI13/19                          | PFI14/51                           | PFI15/17             |

| Start St                      |            |          | Ctr4              | PFI16/49                                | PFI17/15                          | PFI18/47                           | PFI19/13             |

|                               |            |          | Ctr5              | PFI20/45                                | PFI21/11                          | PFI22/43                           | PFI23/9              |

|                               |            |          | Ctr6              | PFI24/41<br>PFI28/37                    | PFI25/7<br>PFI29/3                | PFI26/39<br>PFI30/35               | PFI27/5<br>PFI31/1   |

|                               |            |          | Ctr7              |                                         |                                   |                                    |                      |

Click **Start** to start counting by rising edge. The result is shown below:

Figure 12 Edge Counting In Continuous Mode

- > The numbers are stored in a buffer **Counts**.

- Change the Sample Clock Source to Implicit:

| PCI                            | e/PXIe-5   | 211 CI            | Edge Count                              | ing in F                          | inite                              |                           |

|--------------------------------|------------|-------------------|-----------------------------------------|-----------------------------------|------------------------------------|---------------------------|

|                                |            | Index             |                                         | Counts                            |                                    |                           |

| Slot Number                    | 0 ~        | ▶ 0               |                                         | 1                                 |                                    |                           |

|                                | · ·        | 1                 |                                         | 2                                 |                                    |                           |

| Counter                        | 0 ~        | 2                 |                                         | 3                                 |                                    |                           |

| Initial Count                  | 0          | 3                 |                                         | 4                                 |                                    |                           |

| initial coult                  | •          | 4                 |                                         | 5                                 |                                    |                           |

| Active Edge                    | Rising ~   | 5                 |                                         | 6                                 |                                    |                           |

|                                |            | 6                 |                                         | 7                                 |                                    |                           |

| Direction                      | CountUp ~  | 7                 |                                         | 8                                 |                                    |                           |

| Pause Active Polarity          | None       | 8                 |                                         | 9                                 |                                    |                           |

|                                | None v     | * 9               |                                         | 10                                |                                    |                           |

| Sample Clock Source            | Implicit ~ | * 3               |                                         | 10                                |                                    |                           |

|                                |            |                   |                                         |                                   |                                    |                           |

| Expected Sample Rate           | 10 ≑       |                   |                                         |                                   |                                    |                           |

| External Sample Clock Terminal | PFI33 V    |                   |                                         |                                   |                                    |                           |

| Samples to Acquire             | 10 🜩       |                   |                                         |                                   |                                    |                           |

| Out Event Threshold            | 4294967295 | Counter<br>Number | Signal to Measure(Source)<br>(Name/Pin) | Pause Trigger(Gate)<br>(Name/Pin) | Count Direction(Aux)<br>(Name/Pin) | Output(Out)<br>(Name/Pin) |

|                                |            | Ctr0              | PFI0/65                                 | PFI1/31                           | PFI2/63                            | PFI3/29                   |

|                                |            | Ctr1              | PFI4/61                                 | PFI5/27                           | PFI6/59                            | PFI7/25                   |

|                                |            | Ctr2              | PFI8/57                                 | PFI9/23                           | PFI10/55                           | PFI11/21                  |

|                                |            | Ctr3              | PFI12/53                                | PFI13/19                          | PFI14/51                           | PFI15/17                  |

| Start Sto                      |            | Ctr4              | PFI16/49                                | PFI17/15                          | PFI18/47                           | PFI19/13                  |

|                                |            | Ctr5              | PFI20/45                                | PFI21/11                          | PFI22/43                           | PFI23/9                   |

|                                |            | Ctr6              | PFI24/41<br>PFI28/37                    | PFI25/7<br>PFI29/3                | PFI26/39<br>PFI30/35               | PFI27/5<br>PFI31/1        |

| Avaialble Samples: 10          |            | Ctr7              | PFI28/37                                | PFI2973                           | PFI30/35                           | PFI31/1                   |

Figure 13 Edge Counting With Implicit Clock

- > The numbers are stored in a buffer **Counts.**

- The counter values are different as before because of the change from Sample Clock Source.

### 4.2.2 Pulse Measurement

The counter measures the high-level and low-level duration of a pulse on a signal. Default, the input signal must be connected to Counter Gate terminal.

Set JY5211CITask.Type to CIType.Pulse to use this function.

### Timing

1) Single Mode

The counting value of the duration of the high-level or low-level is written to the register on each rising or falling edge of the pulse to measure, as shown in Figure 14.

Figure 14 Pulse Measurement in Single Mode

To configure the counter to work in this mode, set JY5211CITask.Mode to CIMode.Single.

2) Finite/Continuous Mode with Explicit Sample Clock

The counting value of the duration of the high-level or low-level is stored into the buffer on each rising edge of the sample clock, as shown in Figure 15.

Figure 15 Pulse Measurement with Explicit Sample Clock

To configure the counter to work in this mode, set JY5211CITask.Mode to CIMode.Finite or CIMode.Continuous, and set JY5211CITask.SampleClock.Source to CISampleClockSource.Internal or CISampleClockSource.External.

3) Finite/Continuous Mode with Implicit Sample Clock

In implicit mode, the signal active edge as the implicit sample clock edge. The counting value of the duration of the high-level or low-level is stored into the buffer on each rising edge of the measured pulse, as shown in Figure 16.

Figure 16 Pulse Measurement with Implicit Sample Clock

To configure the counter to work in this mode, set JY5211CITask.Mode to CIMode.Finite or CIMode.Continuous, and set JY5211CITask.SampleClock.Source to CISampleClockSource.Implicit.

#### Timebase

By default, the counter uses the onboard 200MHz timebase to measure pulses. Use the property JY5211CITask.PulseMeas.Timebase to configure the timebase.

Please refer to chapter 4.4.3 for more information about timebase.

### Terminals

To change the terminal of signals instead of using its default value shown in chapter 2.6, use following properties:

- JY5211CITask.PulseMeas.InputTerminal Signal-to-measure input terminal.

- JY5211CITask.PulseMeas.Timebase.External.Terminal External timebase input terminal.

### Learn by Examples 4.2.2

- Connect the signal source's positive terminal Ch1 to PCIe/PXIe-5211 counter0's pulse measure source (CTR0\_Gate, Pin#31), negative terminal to the ground (GND, Pin#32) as shown in Table 2-15 Pin Defination. (CTR0\_Gate, GND) consists of a pulse measure counter input.

- Set the signal source Ch1's output to squarewave signal (f=1Hz, Duty Cycle=50%,  $V_H$ =3.3v,  $V_L$ =0v).

### Single Mode

Open Counter Input-->Winform CI Single Pulse, set the following numbers as shown:

| PCIe/PXIe-5211 CI Pulse in Single Mo | de             |        |                   |                                       | - 🗆 X                                   |

|--------------------------------------|----------------|--------|-------------------|---------------------------------------|-----------------------------------------|

| PCIe/PXI                             | e-5211         | CI     | Pulse i           | n Single                              | e                                       |

| Slot Number<br>Counter               | 0              | ~      | Counter<br>Number | Signal to Measure(Gate)<br>(Name/Pin) | External Timabase(Source)<br>(Name/Pin) |

| Timebase Source                      | Internal200MHz | ~      | Ctr0              | PFI1/31                               | PFI0/65                                 |

| External Timebase Frequency          | 1000000        | ×<br>v | Qr1               | PFI5/27                               | PFI4/61                                 |

| High-Level Duration (s)              |                |        | Qr2               | PFI9/23                               | PF18/57                                 |

| Low-Level Duration (s)               |                |        | Ctr3              | PFI13/19                              | PFI12/53                                |

| Dow Dovor Datation (b)               |                |        | Ctr4              | PFI17/15                              | PFI16/49                                |

|                                      | _              |        | Ctr5              | PFI21/11                              | PFI20/45                                |

| Start                                | Stop           |        | Ctr6              | PFI25/7                               | PFI24/41                                |

|                                      |                |        | Qtr7              | PFI29/3                               | PFI28/37                                |

|                                      |                |        |                   |                                       | .:                                      |

Figure 17 Pulse Measure In Single Mode

> The table in the sample program is a connection diagram for your convenience.

Click Start to start measuring the pulses. The result is shown by High-Level Duration (s) and Low-Level Duration (s):

| PCIe/PXI                    | e-5211 CI        | Pulse i           | n Single                              | е                                      |

|-----------------------------|------------------|-------------------|---------------------------------------|----------------------------------------|

| Slot Number<br>Counter      | 0 ~              | Counter<br>Number | Signal to Measure(Gate)<br>(Name/Pin) | External Timabase(Source<br>(Name/Pin) |

| Timebase Source             | Internal200MHz V | Qtr0              | PF11/31                               | PFI0/65                                |

| External Timebase Frequency | 1000000          | Qtr1              | PF15/27                               | PF14/61                                |

| High-Level Duration (s)     | 0.499741955      | Qtr2              | PF19/23                               | PF18/57                                |

| Low-Level Duration (s)      | 0.500230235      | Qtr3              | PFI13/19                              | PFI12/53                               |

|                             |                  | Ctr4              | PFI17/15                              | PFI16/49                               |

|                             |                  | Qtr5              | PFI21/11                              | PF120/45                               |

| Start                       | Stop             | Ctr6              | PFI25/7                               | PFI24/41                               |

|                             |                  | Qtr7              | PFI29/3                               | PF128/37                               |

Figure 18 Pulse Measure Value In Single Mode

The numbers show the duration of High/Low Level in one signal period and match the duty cycle set before.

### Finite/Continuous Mode

- Change the frequency of the squarewave to 50 Hz.

- Open Counter Input-->Winform CI Finite/Continuous Pulse, set the following numbers as shown:

| PCIe/PXIe-5211 CI Pulse in Finite Ma | ode            |          |                   |                                       | - 🗆 X                                   |

|--------------------------------------|----------------|----------|-------------------|---------------------------------------|-----------------------------------------|

| PCIe/                                | PXIe-5         | 211      | CI Pulse          | e in Finite                           |                                         |

| Slot Number                          | 0              | ~        |                   |                                       |                                         |

| Counter                              | 0              | <u> </u> |                   |                                       |                                         |

| Timebase Source                      | Internal200MHz | ~        |                   |                                       |                                         |

| External Timebase Frequency          | 1000000        | A.       |                   |                                       |                                         |

| Sample Clock Source                  | Internal       | ~        |                   |                                       |                                         |

| Sample Rate                          | 10             | ÷        |                   |                                       |                                         |

| External Sample Clock Terminal       | PFI33          | ~        |                   |                                       |                                         |

| Samples to Acquire                   | 10             | ÷        |                   |                                       |                                         |

|                                      |                |          |                   |                                       |                                         |

|                                      |                | - 81     |                   |                                       |                                         |

|                                      |                |          |                   |                                       |                                         |

|                                      |                |          | Counter<br>Number | Signal to Measure(Gate)<br>(Name/Pin) | External Timabase(Source)<br>(Name/Pin) |

| Start St                             | op             |          | Ctr0<br>Ctr1      | PFI1/31<br>PFI5/27                    | PFI0/65<br>PFI4/61                      |

|                                      |                |          | Ctr2              | PE19/23                               | PFI8/57                                 |

|                                      |                |          | Ctr3<br>Ctr4      | PFI13/19<br>PFI17/15                  | PF112/53<br>PF116/49                    |

|                                      |                |          | Ctr5              | PFI21/11                              | PE120/45                                |

|                                      |                |          | Ctr6<br>Ctr7      | PE125/7<br>PE129/3                    | PF124/41<br>PF128/37                    |

Figure 19 Pulse Measure In Finite Mode

- > The table in the sample program is a connection diagram for your convenience.

- Click Start to begin the finite/continuous pulse measurement. The result is shown below:

| PCIe/                         | PXIe-          | 521      | 1        |              | se in Finite            | 2                      |

|-------------------------------|----------------|----------|----------|--------------|-------------------------|------------------------|

|                               |                |          |          | Index        | High Level Time(us)     | Low Level Time(us)     |

| Slot Number                   | 0              |          | <b>•</b> | 0            | 9994.83                 | 10004.62               |

| JOI MUMBER                    | 0              | ~        | Ľ        | 1            | 9994 83                 | 10004.61               |

| Counter                       | 0              |          |          | 1            |                         |                        |

| ounter                        | 0              | ~        |          | 2            | 9994.83                 | 10004.625              |

|                               |                |          |          | 3            | 9994.835                | 10004.61               |

| imebase Source                | Internal200MHz | ~        |          | 4            | 9994.835                | 10004 61               |

|                               |                |          | <u> </u> |              |                         |                        |

| xternal Timebase Frequency    | 1000000        |          |          | 5            | 9994.835                | 10004.61               |

|                               |                |          |          | 6            | 9994.83                 | 10004.61               |

| ample Clock Source            | Internal       | ~        |          | 7            | 9994.82                 | 10004.62               |

|                               |                |          |          | 8            | 9994.83                 | 10004.61               |

| ample Rate                    | 10             | <b>÷</b> | <u> </u> |              |                         |                        |

|                               |                |          | •        | 9            | 9994.825                | 10004.62               |

| xternal Sample Clock Terminal | PEI33          |          |          |              |                         |                        |

| -                             |                |          |          |              |                         |                        |

| amples to Acquire             | 10             | <b></b>  |          |              |                         |                        |

| ampies to nequire             | IV             | -        |          |              |                         |                        |

|                               |                |          |          |              |                         |                        |

|                               |                |          |          |              |                         |                        |

|                               |                |          |          |              |                         |                        |

|                               |                |          |          |              |                         |                        |

|                               |                |          |          | Counter      | Signal to Measure(Gate) | External Timabase(Sour |

|                               |                |          |          | Number       | (Name/Pin)              | (Name/Pin)             |

|                               |                |          |          | Ctr0         | PFI1/31                 | PFI0/65                |

| Start St                      |                |          |          | Ctr1         | PFI5/27                 | PF14/61                |

| Start St                      |                |          |          | Ctr2         | PFI9/23                 | PF18/57                |

|                               |                |          |          | Ctr3<br>Ctr4 | PFI13/19<br>PFI17/15    | PFI12/53<br>PFI16/49   |

|                               |                |          |          | Ctr4<br>Ctr5 | PFI17/15<br>PFI21/11    | PF120/49<br>PF120/45   |

|                               |                |          |          |              |                         |                        |

|                               |                |          |          | Ctr5<br>Ctr6 | PFI21/11<br>PFI25/7     | PFI20/45<br>PFI24/41   |

#### Figure 20 Pulse Measure Values In Finite Mode

The numbers show the duration of High/Low Level in one signal period and match the duty cycle set before.

Please refer to **Learn by Examples 4.3.1 Finite/Continuous Mode** about the difference between *Explicit* and *Implicit*.

### 4.2.3 Frequency Measurement

The counter measures the frequency of the signal. Default, the measured signal must be connected to Counter Gate terminal.

Set JY5211CITask.Type to CIType.Frequency to use this function.

### Timing

1) Single Mode

Frequency Measurement without sample clock is actually using Pulse Width Measuement internally, refer to chapter 4.2.2 for more information.

Every time the user reads the data, driver will automatically calculate the frequency  $(f_x)$  according to the HighTick  $(tick_h)$ , LowTick  $(tick_l)$  values and known frequency of the timebase  $(f_{base})$  according to the fomular and return the signal frequency to the user.

$$f_x = f_{base} \times \frac{1}{tick_h + tick_l}$$

To configure the counter to work in this mode, set JY5211CITask.Mode to CIMode.Single.

2) Finite/Continuous Mode with Explicit Sample Clock (Averaging)

Between every two rising edges of the sample clock, the counter counts the number of full periods (T1) of the signal, and the number of rising edges of timebase (T2) during those full periods. These two values are stored into the buffer on each rising edge of the sample clock, as shown in Figure 21.

Figure 21 Frequency Measurement with Explicit Sample Clock